完善资料让更多小伙伴认识你,还能领取20积分哦, 立即完善>

5.0共3个课时1781人已学习

讲师:郑振宇 PCB设计总监

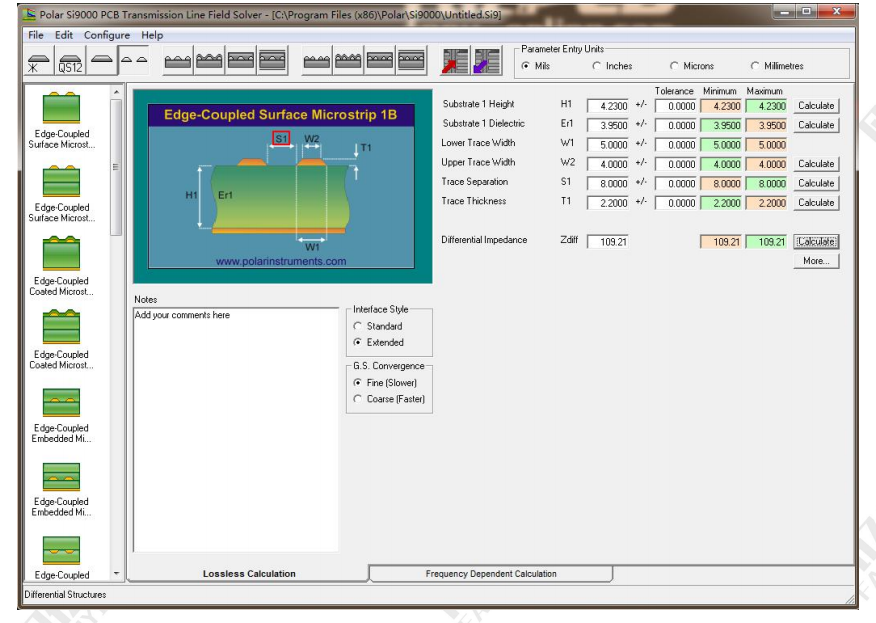

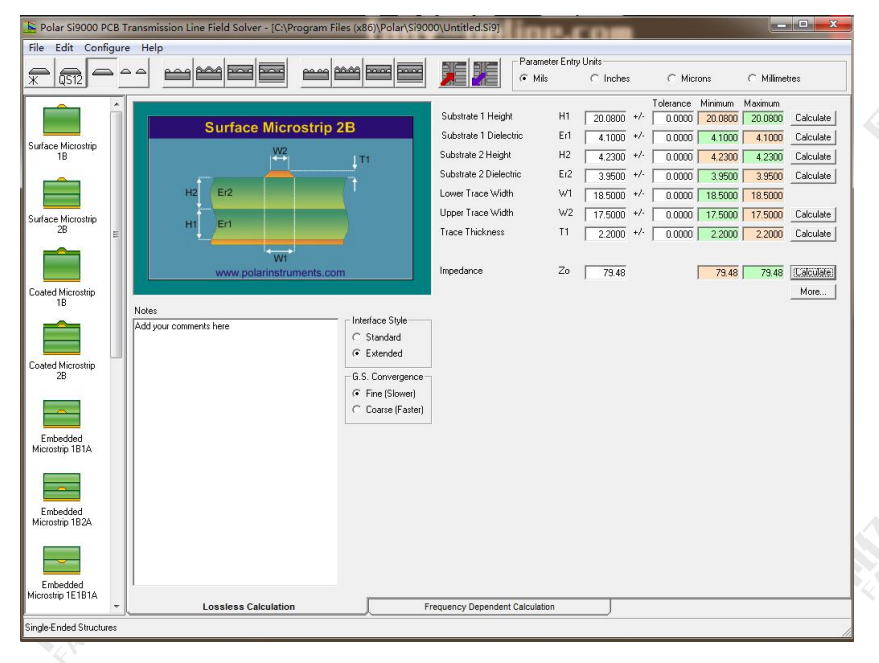

1、掌握常见叠层的阻抗模型 2、掌握如何根据新盘厚度和PP片厚度叠层出要求的厚度板 3、掌握利用SI9000计算阻抗值的方法

随着PCB信号切换速度不断增长,当今的PCB设计厂商需要理解和控制PCB迹线的阻抗。相应于现代数字电路较短的信号传输时间和较高的时钟速率,PCB迹线不再是简单的连接,而是传输线。

在实际情况中,需要在数字边际速度高于1ns或模拟频率超过300Mhz时控制迹线阻抗。PCB迹线的关键参数之一是其特性阻抗(即波沿信号传输线路传送时电压与电流的比值)。印制电路板上导线的特性阻抗是电路板设计的一个重要指标,特别是在高频电 路的PCB设计中,必须考虑导线的特性阻抗和器件或信号所要求的特性阻抗是否一致,是否匹配。所以在PCB设计中我们就必须考虑到阻抗匹配的概念 对设计的走线线宽进行计算!!是高速设计的必备环节

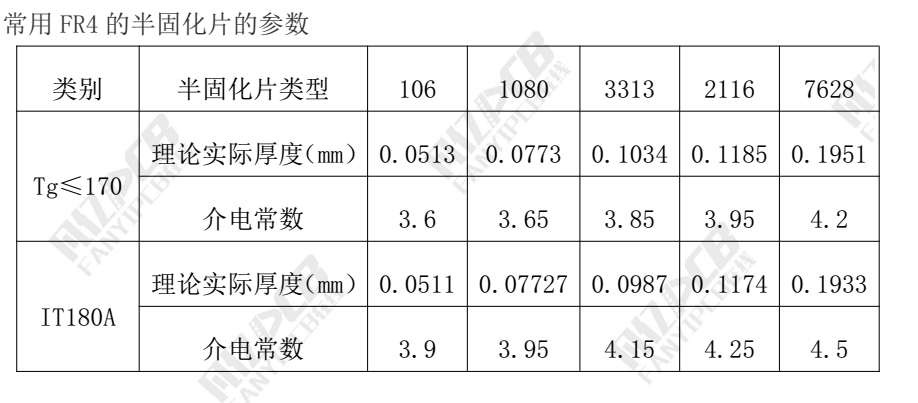

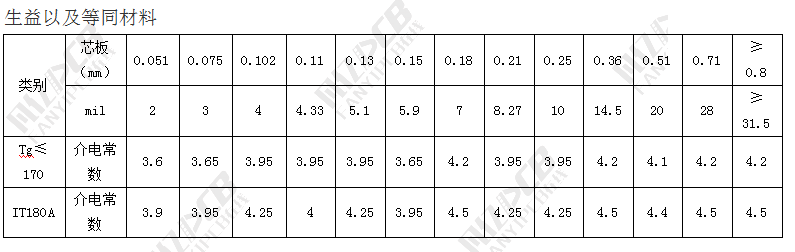

叠层和阻抗设计在每个高速PCB设计当中都需要用到,很多网友老是在问我的板子的走线需要走多宽?差分线的线宽和间距怎么走?我怎么知道他是控制多少阻抗?此视频就是针对这些问题进行解答,并进行实例演示。视频讲解了常见的叠层阻抗模型及列出来了常见板材的芯板(Core)厚度、PP片厚度参数,讲解了如何正确的选择模型并根据阻抗要求计算线宽和间距大小。

6层板的阻抗计算是一个比较典型的节点,作者选此案例对大家进行一个详尽的讲解,这样大家也不用老是纠结自己板子的走线线宽间距的情况了,视频提供的案例大家可以多计算练习下,然后和我们视频讲解的对比一下,不懂的可以直接问我们。

学习完我们的视频之后,可以加入到我们的售后服务群,方便大家技术交流和我们的售后技术,视频的案例完成了的和没完成的都可以找客服索要,方便自己练习之用!同时也可以认识更多行业的朋友,为自己拓宽下人脉,最后祝各位学习的朋友新的一年梦想成真,赚到更多钱,完成自己新一年定的目标,学习是对自己的投资,学会PCB设计可以对自己的工资或者事业都有很大的促进作用的,如果再不努力2017年又到来了,给自己定个目标吧 !

学习目标:

1、掌握常见叠层的阻抗模型

2、掌握如何根据新盘厚度和PP片厚度叠层出要求的厚度板

3、掌握利用SI9000计算阻抗值的方法

详细阻抗计算的概念、叠层的参数、利用SI9000如何计算阻抗

第一部分:阻抗知识详细介绍

1、特性阻抗的定义

特性阻抗:又称“特征阻抗”,它不是直流电阻,属于长线传输中的概念。在高频范围内,信号传输过程中,信号沿到达的地方,信号线和参考平面(电源或地平面)间由于电场的建立,会产生一个瞬间电流,如果传输线是各向同性的,那么只要信号在传输,就始终存在一个电流I,而如果信号的输出电平为V,在信号传输过程中,传输线就会等效成一个电阻,大小为V/I,把这个等效的电阻称为传输线的特性阻抗Z。信号在传输的过程中,如果传输路径上的特性阻抗发生变化,信号就会在阻抗不连续的结点产生反射。影响特性阻抗的因素有:介电常数、介质厚度、线宽、铜箔厚度。

2、控制阻抗的目的

随着信号传送速度迅猛的提高和高频电路的广泛应用,对印刷电路板也提出了更高的要求。印刷电路板提供的电路性能必须能够使信号在传输过程中不发生反射现象,信号保持完整,降低传输损耗,起到匹配阻抗的作用,这样才能得到完整、可靠、精确、无干扰、噪音的传输信号。

阻抗匹配在高频设计中是很重要的,阻抗匹配与否关系到信号的质量优劣。而阻抗匹配的目的主要在于传输线上所有高频的微波信号皆能到达负载点,不会有信号反射回源点。因此,在有高频信号传输的PCB板中,特性阻抗的控制是尤为重要的。

3、计算阻抗需要的条件

板厚、层数、基板材料、表面工艺、阻抗值、阻抗公差、铜厚。

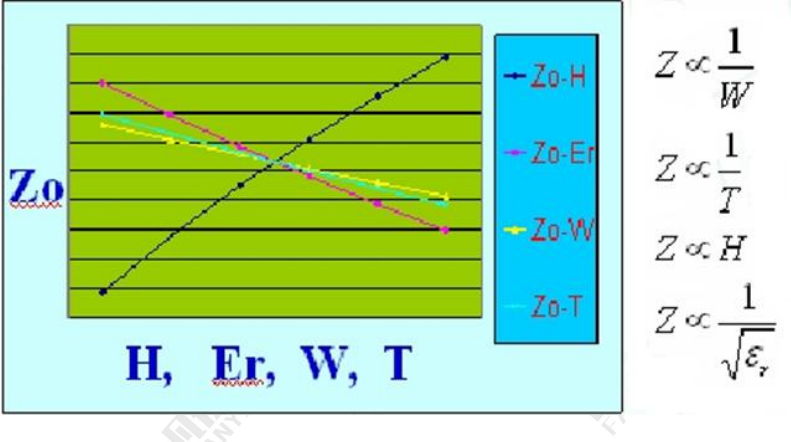

4、影响阻抗的因素

介质厚度、介电常数、铜厚、线宽、线距、阻焊厚度

一般,介质厚度、线距越大阻抗值越大;介电常数、铜厚、线宽、阻焊厚度越大阻抗值越小。

①介质厚度 H

增加介质厚度可以提高阻抗,降低介质厚度可以减小阻抗;不同的半固化片有不同的胶含量与厚度.其压合后的厚度与压机的平整性、压板的程序有关;对所使用的任何一种板材,要取得其可生产的介质层厚度,利于设计计算,而工程设计、压板控制、来料公差是介质厚度控制的关键。

②线宽 W

增加线宽,可减小阻抗,减小线宽可增大阻抗。线宽的控制要求在+/-10%的公差内,才能较好达到阻抗控制要求信号线的缺口影响整个测试波形,其单点阻抗偏高,使其整个波形不平整,阻抗线不允许补线,其缺口不能超过10%

线宽主要是通过蚀刻控制来控制。为保证线宽,根据蚀刻侧蚀量、光绘误差、图形转移误差,对工程底片进行工艺补偿,达到线宽的要求。

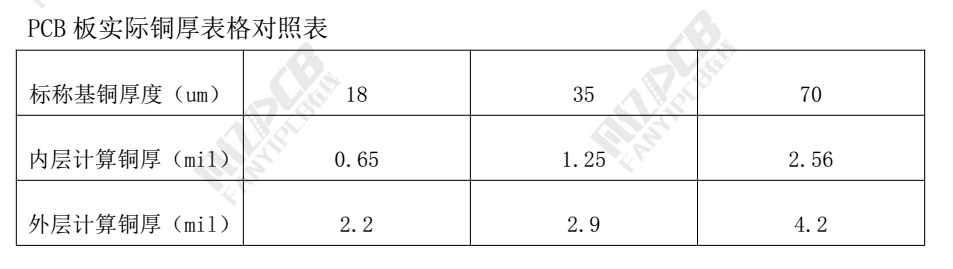

③铜厚 T

减小线厚可增大阻抗,增大线厚可减小阻抗;线厚可通过图形电镀或选用相应厚度的基材铜箔来控制。对铜厚的控制要求均匀,对细线、孤立的线的板加上分流块,其平衡电流,防止线上的铜厚不均,影响阻抗对cs与ss面铜分布极不均的情况,要对板进行交叉上板,来达到二面铜厚均匀的目的。

④介电常数 Er

增加介电常数,可减小阻抗,减小介电常数可增大阻抗,介电常数主要是通过材料来控制。不同板材其介电常数不一样,其与所用的树脂材料有关:FR4板材其介电常数为3.9—4.5,其会随使用的频率增加减小,聚四氟乙烯板材其介电常数为2.2—3.9间要获得高的信号传输要求高的阻抗值,从而要低的介电常数。

⑤阻焊厚度

印上阻焊会使外层阻抗减少。正常情况下印刷一遍阻焊可使单端下降2欧姆,可使差分下降8欧姆,印刷2遍下降值为一遍时的2倍,当印刷3次以上时,阻抗值不再变化。

第二部分:层叠计算、参数计算、阻抗计算

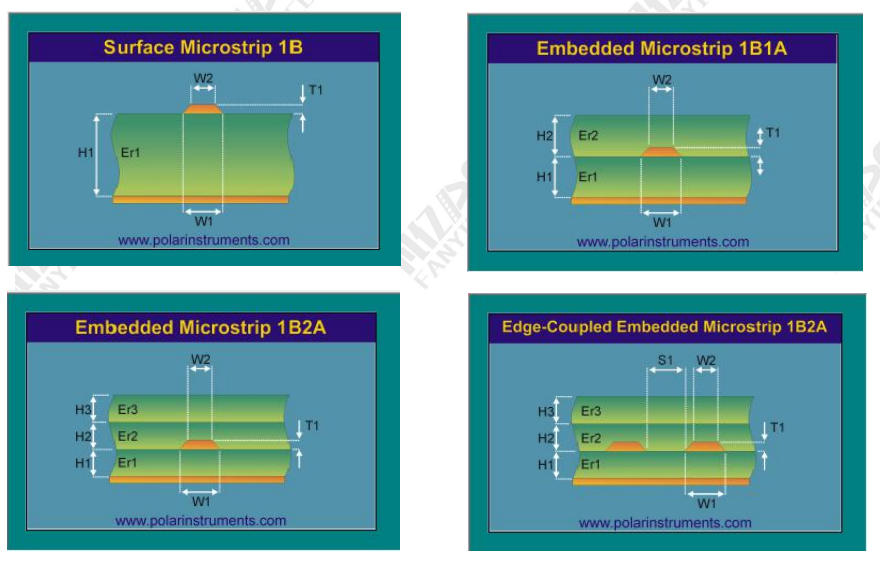

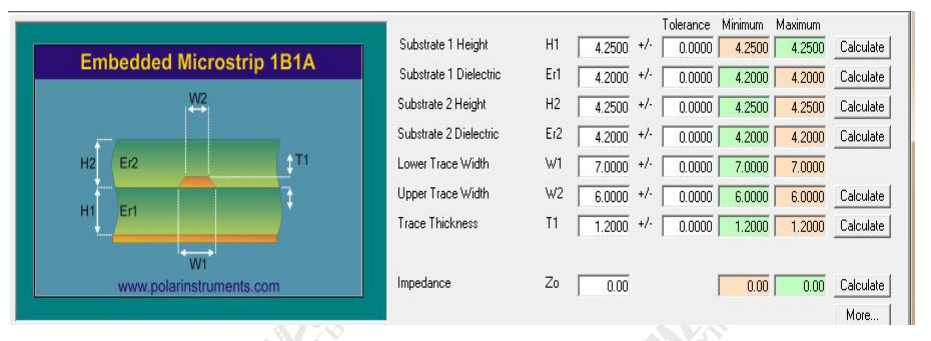

1、阻抗计算模式

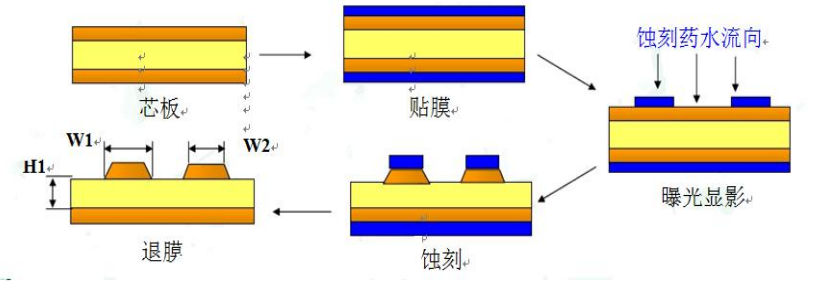

如上图所示,由于生产中蚀刻药水对铜表面接触的充分,而与下方接触相对较弱,因此蚀刻出来的线宽呈梯形,且W1>W2。

从图中可知,下线宽W1所接触的介质为芯板,因此阻抗计算软件中的H1值即为芯板厚度。

3、阻抗设计常用参数

注:多种半固化片组合的介电常数取其算术值;板厚精度根据来料实测厚度,阻抗设计计算叠层厚度与层间介质层厚度时按来料实际厚度及根据线路分布率进行计算。

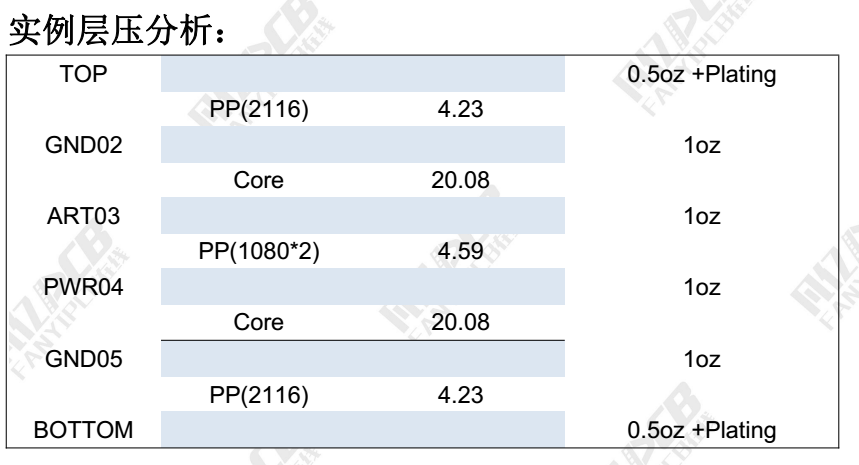

4、板子层压实际厚度计算(6层板为例)

层压板厚=内外层的铜厚+PP片的厚度+芯板的厚

计算公式

计算公式

类型一:实测厚度=理论厚度-铜厚*(1-残铜率)

类型二:实测厚度=理论厚度-铜厚1*(1-残铜率1)-铜厚2*(1-残铜率2)

注:残铜率:残铜率是指板平面有铺铜的面积和整板面积之比;一般表层的残铜率取100%。光板的残铜率为0,一般我们设计中平面层取残铜率65%,信号层取残铜率15%。

2116厚度=0.1185*39.37-1.25*(1-0.65)=4.23mil

1080*2厚度=0.0773*2*39.37-1.25*(1-0.15)-1.25*(1-0.65)=4.59mil

层压板厚=2.2*2+4.23+20.08+4.59+20.08+4.23+1.25*4=62.61mil=1.59mm

第三部分:6层板阻抗计算实例演示(视频)

表层阻抗=SI9000软件计算值(不盖阻焊模式)*0.9+3.2

内层阻抗= SI9000软件计算值

L1/6层单端50欧姆走线

L3层单端50欧姆走线

L1/6层差分100欧姆走线

L3层差分100欧姆走线

L1层单端75欧姆、隔层参考L3层走线

L1/L6 微带线、共面阻抗100欧姆走线

时长:77分钟 大小:100MB

讲师:郑振宇 5.06141人已学习

¥28.80

原价¥29.90

讲师:郑振宇 5.017910人已学习

¥159.00

原价¥376.20

讲师:郑振宇 5.026760人已学习

¥68.00

原价¥136.25

讲师:郑振宇 4.820561人已学习

¥28.80

原价¥57.42

讲师:郑振宇 4.915823人已学习

¥199.00

原价¥398.08

专栏评论

课程评分